- Tutorial

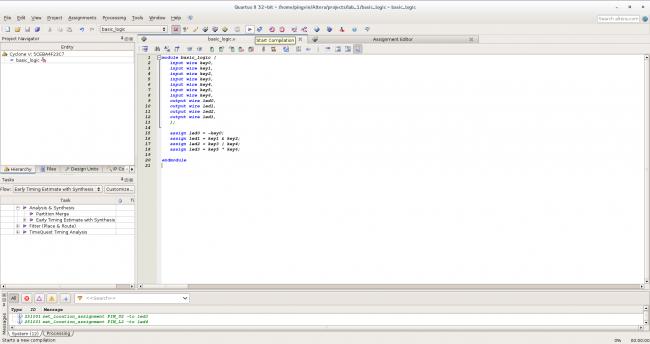

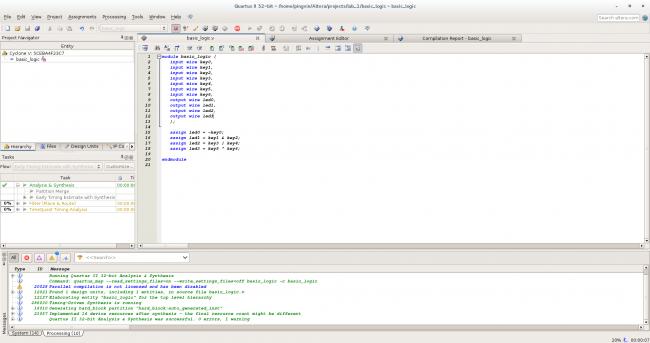

Продолжаем осваивать FPGA Altera. В первой части я описал процесс установки программного обеспечения Altera Quartus под CentOS7. Теперь уже наконец попробуем что-то сделать «железное», например светодиодики позажигаем. Но прежде небольшое вступление. Одним из направлений моей деятельности является преподавание в кружке робототехники в небольшом городке Беларуси. Окунувшись во всю эту кухню и поучаствовав в разных конкурсах не только как тренер команды, но и как судья, я пришел к выводу, что ардуино в частности и микроконтроллеры в целом не самая лучшая база для конкурсных роботов (про лего вообще молчу). Многие задачи эффективней решать на уровне голой электроники. Кроме того 90% процентов кружков и «школ» робототехники не дают даже базовых знаний именно электроники, сосредоточившись чисто на «обучении» программированию готовых конструкций. Но чисто электронные роботы (например незаслуженно забытые BEAM) заточены под конкретную задачу и изменение условий конкурса приведет к необходимости существенной перестройки робота, что не всегда возможно. Вот тут я и вспомнил про программируемую логику. В результате поиска информации о применении ПЛИС в обучении я наткнулся на блог Юрия Панчула . Пользуясь случаем я хочу публично выразить ему свою благодарность. Благодаря ему наш кружок совершенно бесплатно получил плату TerasIC DE0-CV c Altera Cyclone V на борту. Собственно эта и последующие публикации будут представлять собой реальный учебный материал, который мы реализовываем на кружке. И я буду благодарен за конструктивную критику и замечания, так как применение ПЛИС на кружках для школьников — нехоженая пока область. Итак, начинаем. В этой публикации будут описаны первые шаги в Quartus, описание элементарной цифровой логики на языке Verilog и загрузка конфигурации в FPGA Altera Cyclone V. Работать мы будем с платой TerasIC DE0-CV, которая имеет на борту встроенный USB-Blaster. Так же затронем и вопрос «запуска» USB-Blaster под Linux. Запускаем Quartus:

dmesg | tail Переходим в папку /etc/profile.d/ , где создаем файл custom.sh А затем в папке /etc/udev/rules.d/ файл с названием 51-usbblaster.rules И наполняем его смыслом: Теперь все работает и прошивка прекрасно вгружается в чип: Любуемся результатом, играемся переключателями, мигая светодиодиками:

- Цена: $13.68

Обзор программатора для ПЛИС фирмы Altera. Кому интересно — прощу под кат.ПРЕДУПРЕЖДЕНИЕ: данный обзор написан для тех, кто «в теме». Если об электронике и ПЛИСах Вы имеете смутное представление, то, судя по комментариям, этот обзор будет врятли Вам полезен. USB-Blaster — программатор, разработанный фирмой Altera для своих ПЛИС. Имеет три интерфейса программирования: JTAG, Active Serial и Passive Serial. Предназначен для программирования и отладки ПЛИС этой фирмы. По просьбам привожу некоторые расшифровки: — ПЛИС(FPGA или CPLD) — Программируемая логическая интегральная схема. — Altera — американская компания, один из ведущих и крупнейших производителей ПЛИС — Cyclone II — семейство FPGA этой фирмы. — Altera Quartus II — САПР, разработанная Альтерой для проектирования и отладки своих ПЛИС. — JTAG — грубо говоря, интерфейс для программирования и отладки сложных цифровых микросхем и устройств. На данный момент — промышленный стандарт. — AS и PS — интерфейсы программирования последовательных конфигурационных ПЗУ. Данный программатор покупался для и одновременно с Отладочной платой на кристалле Cyclone II( mysku.ru/blog/aliexpress/12915.html )год назад. Надо сказать, что китайцы очень и очень приятно удивили своей ценой. Для сравнения: цена у оф. производителя — 300$, цена у стороннего производителя(Terasic) — 100$(сейчас уже 50$), цена в Питерском магазине Терраэлектроника — примерно 16000 рублей. В итоге экономия от 10 до 40 раз. Данных по трекингу у меня уже нет, т.к. заказывал не я, но посылка дошла примерно за 25-30 дней.Фото

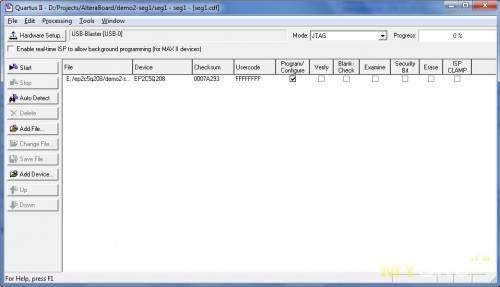

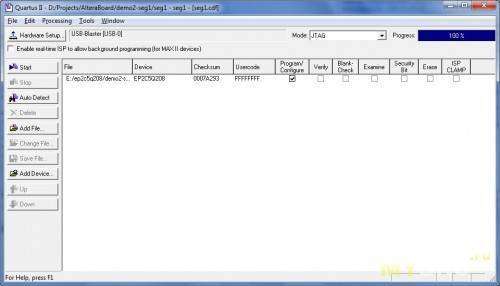

Сделан он на четверочку — внешний вид сразу выдает китайскую подделку. Но мы ведь им не любоваться будем, а работать. И в плане работы он хорош. ПО Quartus II принял его как родного Ну и процесс прошивания:Дополнительная информация Плюсы: + Цена + Цена + ЦЕНА! + Полная совместимость с оригинальным устройством. Прошивание и отладка через jtag работают отлично. Минусы: — «Китайский» внешний вид. — Некорректно работает интерфейс AS, НО тут неизвестно кто виноват — USB-Blaster или моя отладочная плата. К покупке настоятельно рекомендую! 20.02.18 AlexD 10 304 12 В тот момент, когда почти все типы ЦАП изготовлены и отслушаны, пощупаны и попробованы на вкус, возникает вопрос: «А что дальше-то?»С малых лет у меня была особенность — мне интересен процесс, а не результат. Поэтому все мои поделки либо раздаются, либо разбираются, либо глубоко модернизируются.Естественно возникла шальная идея: а почему бы мне не попробовать ПЛИС?

В тот момент, когда почти все типы ЦАП изготовлены и отслушаны, пощупаны и попробованы на вкус, возникает вопрос: «А что дальше-то?»С малых лет у меня была особенность — мне интересен процесс, а не результат. Поэтому все мои поделки либо раздаются, либо разбираются, либо глубоко модернизируются.Естественно возникла шальная идея: а почему бы мне не попробовать ПЛИС?

Содержание / Contents

Мир цапостроя не заканчивается на РСМ63 или AD1862, а новые форматы и поддерживающие их чипы уже доступны.Это интересно. И не так уж сложно. Достаточно иметь нужный набор инструментов, который стал доступен практически каждому, и желание пробовать и экспериментировать.

↑ Небольшое вступление: CPLD она же ПЛИС

ПЛИС, что расшифровывается как Программируемая Логическая Интегральная Схема, по буржуйски — CPLD, что означает Complex Programmable Logic Device, в цапостроении применяется уже давно. А в мире цифровых устройств еще раньше. Один из моих самосборных компьютеров «Орион-128» имел в стартовом комплекте печатную плату и прошитую ПЛИС, без которой плата бы никогда не запустилась бы. А это было… Ох, уже и не вспомню.Но давно.ПЛИС бывают разные. Основные производители на данный момент — это Xilinx и Altera, ну может кто-то еще — не вдавался. Бывают они разной структуры, назначения, ёмкости. Всего не перечислить. Технологии-то уже более 20 лет… Не беда, лампы вон до сих пор в цене:)

↑ Однако, приступим!

Когда я искал материал по ПЛИС, наткнулся на статью моего тёзки с ником Lexus. Называется она «Использование ПЛИС в DAC». За статью автору огромное спасибо! Возможно это единственный материал, где подробно разжёвано всё от начала и почти до конца. Всёе остальное, включая документацию от производителей, довольно тяжело осваивать «в лоб». Вот на базе этого материала я и расскажу о своём опыте работы с ПЛИС. Я конечно постараюсь покороче, ну, а вы готовьте помидоры и изучайте.Для начала нужно определиться, для чего и как будем использовать этот самый ПЛИС. Задача конвертации RJ в I2S, описанная в вышеуказанной статье — это просто, и как то меня она минула за ненадобностью, а вот коммутация входов, деление частоты на костыле из 3 корпусов 74НС74, переключение генераторов — вот минимальная задача, ради которой стоит начать знакомство с этой технологией.Поэтому за основу был взят готовый ЦАП на AK4137, описанный в моей предыдущей статье. Следующий шаг — обеспечить себя необходимым окружением. Для этого качаем из сети рекомендованный Лексусом Quartus II 9.1 SP 2. Я для интереса скачал самый новый. Не знаю, на любителя. Например, в новой версии отсутствует поддержка устаревших версий ПЛИС (а именно — нужной нам ЕРМ3064), обилие наворотов и обязательная регистрация перед скачиванием (и так спам девать некуда) мне не понравились.Далее покупаем программатор. Или собираем на коленке. Мне оказалось проще купить: USB Blaster (Altera CPLD/FPGA programmer)Можно сначала купить — потом качать Quartus, не важно. У меня например было время немного освоить этот Quartus, пока мой программатор пинали ногами на транзитных пунктах китайской почты.

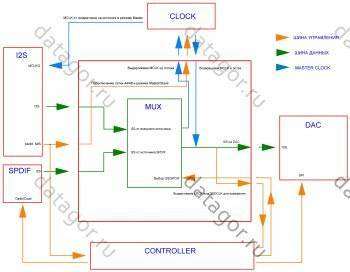

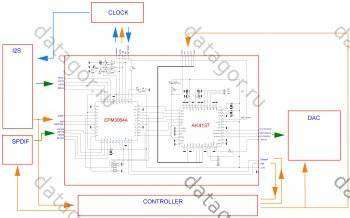

↑ Задача в подробностях

Теперь более подробно расскажу о поставленной перед нами задаче.Итак: простая схема взаимодействия блоков и модулей в среднестатистическом ЦАП показана на рисунке:

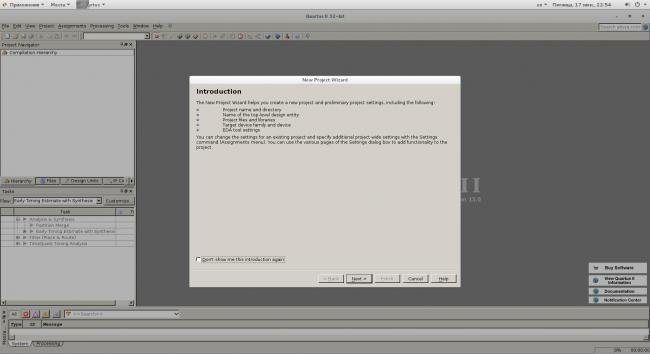

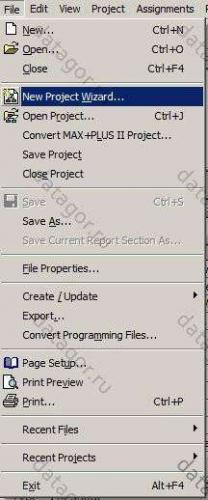

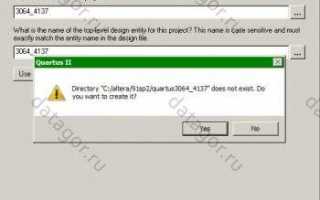

↑ Теперь можно ставить софт и готовить проект

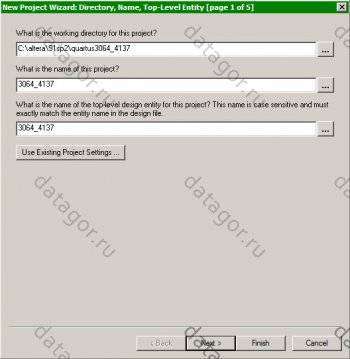

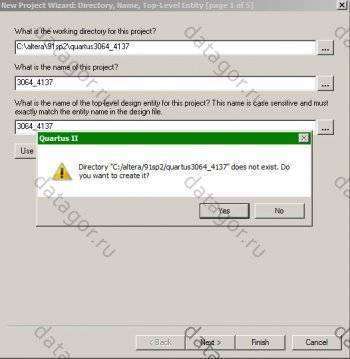

Особенностей установки нет никаких, просто после установки нужно выбрать тип Quartus II для внешнего вида программы. Пути установки по умолчанию.Далее заходим в меню File→New-Project-Wizard.

↑ Все готово. Теперь можно творить!

Для того чтобы сделать мелкую пакость поместить компонент в схему нужно два раза клацнуть на пустом поле редактора где сетка.В поле «Name» набираем 74257. Это мультиплексор 2×4. Далее, обязательно нужно накидать входы и выходы. Для входа набираем input, для выхода — output.По даташиту смотрим логику работы ног (например здесь для разрешения работы надо на OE (или GN) подать лог 0), и подключаем куда надо vcc или gnd. Все это также набирается в поле «Name».Ну и рисуем соединения согласно выбранной схемы. Обязательно нужно дать уникальные имена входам и выходам, чтоб потом не запутаться. Я их назвал по имени сигнала с которым они работают.Должно получиться примерно так: Я сделал проще — я сначала нарисовал схему, и по ней именовал ноги.Так получилось более наглядно.После этого нужно скомпилить проект. Для этого вверху в меню есть треугольный значок с названием «Start compilation».Результат получается примерно такой: Это нормально, главное чтоб не было ошибок и проект скомпилировался.Предупреждения можно игнорировать, они, как правило, связаны с невозможностью провести моделирование поведения схемы. А если полезло красненькое — то косяк серьезный, работать не будет. Здесь же видна суммарная информация — сколько занято ячеек и сколько использовано ног.После этого надо назначить ноги, точнее привязать ноги к конкретным пинам ПЛИС. Для этого лучше использовать рисунок платы: Следует иметь в виду, что ноги для программатора нужно развести на разъем программатора, специальные и неиспользованные ноги нужно оставить висеть в воздухе. Во избежании казусов. В даташите на выбранный тип ПЛИС ноги описаны.Для привязке физических ног к виртуальным используется функция Pin Planner. Это самое шикарное во всем процессе. Не надо думать как и куда развести ноги на плате, просто накидал при разводке платы и назначил в процессе! Pin Planner находится левее кнопки компилятора (чип с карандашом и символом пина).Вот такое окошко: Тут видно наш выбранный в начале проекта чип и его доступные для назначения ноги. Они обозначены кружочками.Внизу список наших имеющихся виртуальных ног.Просто берем node name из левой колонки и назначаем ему location. При этом назначенный пин станет темно красным на рисунке.Вот так.После привязки всех ног окончательная схема выглядит так: Возле входов и выходов появились номера физических ног микросхемы.Тут я поигрался немного с разными типами делителей. И отдельно вывел выход мониторинга шины DATA или DSDL. По ней стоит делитель с нереальным коэффициентом деления аж 262144 на пяти счетчиках 7493. Теперь у меня весело мигает светодиод при передаче данных. Оно конечно нафиг не нужно, но получилось наглядно. Все, готово. Еще раз компилим проект. Если все хорошо — можно пробовать шить, или прошивать нашу плис. Естественно она должна быть припаяна в схему.И на нее надо подать питание.Подключить программатор. Сам программатор можно поставить в систему заранее, драйвера есть в папке с программой %altera91sp2quartusdriversusb-blaster, но питание его выходного буфера производится от платы с ПЛИС, поэтому без питания работать он не будет.Теперь, когда все готово, идем в меню с программатором. Оно тоже вверху.Вот такое окно: Кнопкой Hardware Setup выбираем USB Blaster, тип загрузки — JTAG.Внизу наш проект. Галочками отмечаем нужные опции.Включаем питание ПЛИС и дрожащей рукой нажимаем Start…Процесс идет очень быстро, я даже испугаться не успел. Если что-то прошилось, то внизу в логе будет такое: Можно выдохнуть. Девайс умный. Сам читает тип ПЛИС, так что другой проект просто не зашьется.Также в случае перепутанных/не припаяных ногах программатора будет грязная ругань, что девайс не опознан или проблема программатора.Но это не значит что все заработало как надо. Возможно потребуются коррективы схемы, изменение логики и повторная прошивка. Производителем заявлено 100 циклов перезаписи ПЛИС, мой личный рекорд в этом проекте — 6! А все потому, что я считал например, что у буфера с именем btri, что я использовал как логический аналог 74lvc1g125, вход разрешения работы OE имеет активное состояние лог 1, а оказалось, что это полный аналог 125 го буфера, и OE у него активно при лог 0. Прошивать можно в любой момент, даже в процессе работы ЦАП. Ничего страшного не происходит.Возможное количество прошивок больше 100, но производитель не гарантирует работоспособность ПЛИС при превышении этого порога. Реально можно шить больше и чаще, специалисты проверяли.Но о сотне всегда помнишь и много раз подумаешь, прежде жать кнопку «Старт». При назначении выводов ПЛИС не предусмотрено подключение «подпорок», или подтягивающих резисторов на плюс или минус питания, как это сделано в микроконтроллерах.Также не предусмотрены прочие «аналоговые» заморочки для подключения к стандартной логике. Поэтому все времязадающие конденсаторы, подтягивающие резисторы, и любые другие «аналоговые» компоненты в логике ПЛИС отсутствуют. Все это необходимо предусмотреть заранее — подключить внешние «подтяжки» на нужные ноги ПЛИС или вывести конденсаторы времязадающих цепей на внешние ноги.Иначе никак.Настоящие разработчики делают еще одну «фишку» — формирование SPI для управления ЦАП с помощью ПЛИС.Я, как неспециалист, конечно попытался реализовать подобное на макетной плате на базе EPM240, но получилось немного не так, как хотелось. Точнее получилось г*, и я сразу потерял интерес к этому процессу.Но оно и понятно, тут уже нужно использовать не логические элементы, а описание логики работы на hardware description language (HDL). Он чем то напоминает старый добрый Basic, но моих знаний пока недостаточно для его освоения. К тому же формировать SPI управление на том же STM32/Arduino оказалось проще с точки зрения количества задействованных ног у контроллера и количества проводов в связке ЦАП-МК.То есть выигрыш в формировании SPI в ПЛИС оказался лично для меня пока сомнительным удовольствием. Может потом и освою, а пока по старинке используем контроллер. Ну, а если, к примеру, наш проект окажется большего размера, и не хватит нам ног или ёмкости ПЛИС, можно использовать что-нибудь из серии MAX-II, например EPM240T100C5.Шаг ног там конечно поменьше, зато ног побольше и емкость уже 240 ячеек. Я их зачем-то заказал, но смог нагрузить только на 20%, поэтому, чтоб не валялись, пришлось применять. Вон она, слева от генераторов притаилась.

↑ Итого

Как вы понимаете, применение ПЛИС не ограничивается ЦАП. Наоборот, эту технологию активно применяют там, где нужно сэкономить место и заменить десятки корпусов обычной логики на один корпус ПЛИС. Любой конечный автомат, вроде блока управления вертушкой, механикой, или какие-нибудь электронные часы — это само простое, что пришло в голову.Думаю, данный материал будет полезен многим.Ну, а у меня на сегодня все. Продолжение следует!С уважением, Алексей.

Камрад, смотри полезняхи!

Алексей (AlexD)Алматы, КазахстанСписок всех статейПрофиль AlexD

Читательское голосование

Статью одобрили 66 читателей.

Для участия в голосовании зарегистрируйтесь и войдите на сайт с вашими логином и паролем.

Поделись с друзьями!

Связанные материалы

Аудио ЦАП DAC. Поделки начинающего цапостроителя. Часть 1. pcm2704 + ad822… Когда очень хочется слушать музыку… Я беру в руки перфоратор! Собираем аудиоцап на pcm2704! Когда… Аудио ЦАП DAC. Поделки начинающего цапостроителя. Часть 13. PCM63P-K, о грейде чипов ЦАП… На столе PCM63P-K. Заняться изготовлением данного утройства меня подтолкнуло любопытство. Когда я… Аудио ЦАП DAC. Поделки начинающего цапостроителя. Часть 21, заключительная. АК4137+АК4490 на новой платформе. Итоги долгого пути… Привет, датагорцы! Вы уже собрали, сожгли, повторили один-в-один за автором или даташитом… Fast Stone Image Viewer — удобная бесплатная программа для просмотра и редактирования картинок… Друзья! Сегодня хочу представить вам FastStone Image Viewer — быстрый, стабильный, дружественный к… Самоучитель по радиоэлектронике. Николаенко М. Н…. Николаенко М. Н. Самоучитель по радиоэлектронике. — М.: НТ Пресс, 2006. — 224 с: ил. Вы держите в… Аудио ЦАП DAC. Поделки начинающего цапостроителя. Часть 12. PCM63, AD1862… «Эй, Макфлай! – взвизгнул он. – Никуда не уходи! Ты – следующий!» PCM63 и AD1862. Они пришли одной… CDAID v.3.20 + русский мануал… © 2008 Игорь Котов, перевод, составление, иллюстрации. Возможности программыПрограмма CDAID… Кулинария lossless форматов… С тех пор, как стало возможным представить звук в цифровом виде, появилась возможность обмениваться… Почему я люблю Texas Instruments?… Я люблю Texas Instruments потому, что это мощная корпорация, крупнейший в мире производитель… Аудио ЦАП DAC. Поделки начинающего цапостроителя. Часть 15. Модульный ЦАП с пересинхронизацией. PCM58, PCM63, PCM1701, AD1862, SRC4192, SM5842, SM5843, DF1706, ADUM1100… На столе 74AC245, PCM58 ,PCM63, PCM1701, AD1862, SRC4192, SM5842, SM5843, DF1706, ADUM1100,… Как намотать трансформатор. А.Н. Подъяпольский… Как намотать трансформатор. А.Н. Подъяпольский. Типография Госэнергоиздата. Москва, 1953г. При… Аудио ЦАП DAC. Поделки начинающего цапостроителя. Часть 9. WM8805, WM8740 — приручаем «волчат»… В предыдущей статье я рассказал о работе с цифровыми ресиверами, теперь пора перейти к другому…

Общаемся по статье 💬

Аудио ЦАП DAC. Поделки начинающего цапостроителя. Часть 20. ПЛИС в ЦАП. Quartus II + Altera USB Blaster

Комментарии, вопросы, ответы, дополнения, отзывы

Информация Вы не можете участвовать в комментировании. Вероятные причины: — Администратор остановил комментирование этой статьи. — Вы не авторизовались на сайте. Войдите с паролем. — Вы не зарегистрированы у нас. Зарегистрируйтесь. — Вы зарегистрированы, но имеете низкий уровень доступа. Получите полный доступ.

Используемые источники:- https://habr.com/post/310816/

- https://mysku.ru/blog/aliexpress/12916.html

- https://datagor.ru/audio-dac/2933-make-audio-dac-part-20-plis-pld.html

Обзор усилителя FX AUDIO DAC-X6 с АлиЭкспресс

Обзор усилителя FX AUDIO DAC-X6 с АлиЭкспресс Усилители + ЦАП для наушников / Купить наушники и гарнитуры в интернет-магазине Doctorhead.Ru

Усилители + ЦАП для наушников / Купить наушники и гарнитуры в интернет-магазине Doctorhead.Ru TempoTec Sonata iDSD Plus: пожалуй, лучший ЦАП в своем сегменте

TempoTec Sonata iDSD Plus: пожалуй, лучший ЦАП в своем сегменте