- Цена: $8.90 за две штуки

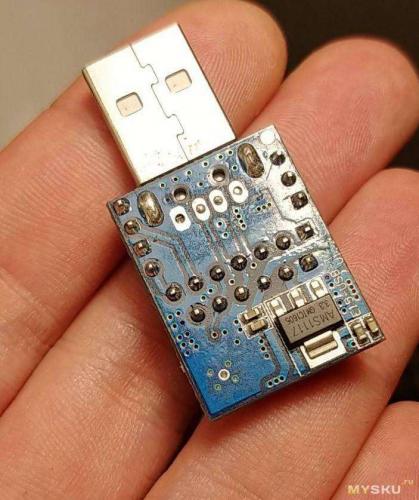

Одна из тех вещей, качественных вещей, которыми пользуешься много лет, и не замечаешь. А когда требуется снова такая, оглядев аналоги — ищешь «только точно такую же» Что такое преобразователь USB- COM любителям и профессионалам объяснять, наверное, не надо. Но обычно, по законам жанра, все же положено вступительное слово. Да и пока подбираешь эти вступительные слова — бывает и сам новое узнаешь. Не буду отступать. Последовательный порт, он же RS-232, он же COM порт, он же стык С2, бандит в общем. Стандарт был принят в 1969 году, когда появился на свет — найти не удалось. Описывает физический уровень передачи информации между… Вот уже не знаю, между чем. Наверное тогда — между ЭВМ. В дальнейшем — и между ЭВМ и периферийными устройствами. И насколько я помню — уровни напряжений составляли дикие +- 12 вольт. +12 — линия неактивна, лог.1, а минус 12 — активна, лог.0 Время шло, COM порт вытеснялся USB, многие прочили смерть COM порта… Как же они были наивны. COM порт живее всех живых, и думаю до конца этого века даже никуда не денется. Во многих современных компьютерах его уже не устанавливают, либо он всего один, и даже не выведен с материнской платой. А оборудования, работающего по этому протоколу много, так что переходники на USB — наше все. Этот переходник я не покупал ранее. Мне его присылала достаточно известная в узких кругах фирма CDSNET. Не побоюсь слова фирма, знаком с их продукцией лет 7 наверное. Присылала не просто так, а как аксессуар к их приемопередатчикам. Эти цифровые трансиверы — весьма качественная штука, запечатленный на фото — по сути радиоудлинитель COM-порта, позволяет передать информацию на расстояние до пары км (зависит от застройки, антенны, скорости передачи). На частоте не смотрите — мне — можно. ))

Деканат

|

ДЕКАНЛОЙ ВЛАДИМИР НИКОЛАЕВИЧ, канд. техн. наук, доцентТел. (факс): 8 (017) 327-10-41E-mail: lid@belstu.byАдрес: ул. Свердлова 13а, к.4, ауд. 214Прием по служебным вопросам: ежедневно, кроме субботы, с 10-00 до 12-00.Прием по личным вопросам: четверг, пятница с 14-00 до 17-30. |

|

| ЗАМЕСТИТЕЛЬ ДЕКАНА по учебной и научной работеРАПОВЕЦ ВЯЧЕСЛАВ ВАЛЕРЬЕВИЧ, канд. техн. наук, доцентТел. (факс): 8 (017) 327-10-41E-mail: lid@belstu.byАдрес: ул. Свердлова 13а, к.4, ауд. 211Прием по служебным вопросам: ежедневно, кроме субботы, с 10-00 до 12-00.Прием по личным вопросам: понедельник, четверг с 14-00 до 17-30. | |

|

ЗАМЕСТИТЕЛЬ ДЕКАНА по идеологической и воспитательной работеКРАСКОВСКИЙ СТАНИСЛАВ ВЛАДИМИРОВИЧ, канд. техн. наук, доцентТел. (факс): 8 (017) 327-10-41E-mail: lid@belstu.byАдрес: ул. Свердлова 13а, к.4, ауд. 211Прием по служебным вопросам: ежедневно, кроме субботы, с 10-00 до 12-00 ч.Прием по личным вопросам: среда с 14.00 до 17.30 ч, суббота с 10.00 до 12.30 ч. |

|

| ДИСПЕТЧЕРХОДОСЕВИЧ ЕЛЕНА АНАТОЛЬЕВНА Тел. (факс): 8 (017) 327-10-41 E-mail: lid@belstu.by Адрес: ул. Свердлова 13а, к.4, ауд. 214 |

Уровни напряжения сигнала логики

Глава 3 — Логические ворота

Цепи логических затворов предназначены для ввода и вывода только двух типов сигналов: «высокий» (1) и «низкий» (0), как представлено переменным напряжением: полное напряжение питания для «высокого» состояния и нулевого напряжения для «низкое» состояние. В идеальном мире все сигналы логической схемы будут существовать при этих предельных значениях напряжения и никогда не отклоняться от них (т. Е. Меньше полного напряжения для «высокого» или более нулевого напряжения для «низкого»). Однако в действительности уровни напряжения логического сигнала редко достигают этих идеальных пределов из-за паразитных падений напряжения в схеме транзистора, и поэтому мы должны понимать ограничения уровня сигнала в схемах затвора, поскольку они пытаются интерпретировать сигнальные напряжения, лежащие где-то между полным напряжением питания и нуль.

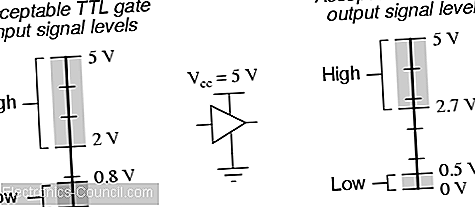

Затворы TTL работают от номинального напряжения питания 5 вольт, +/- 0, 25 вольт. В идеале, «высокий» сигнал TTL должен составлять 5, 00 вольт точно, а TTL «низкий» сигнал 0, 00 вольт точно. Тем не менее, реальные схемы затвора TTL не могут выводить такие идеальные уровни напряжения и предназначены для приема сигналов «высокого» и «низкого», существенно отличающихся от этих идеальных значений. «Приемлемые» напряжения входного сигнала варьируются от 0 до 0, 8 вольт для «низкого» логического состояния и от 2 вольт до 5 вольт для «высокого» логического состояния. «Допустимые» напряжения выходного сигнала (уровни напряжения, гарантированные производителем затвора в заданном диапазоне условий нагрузки) находятся в диапазоне от 0 до 0, 5 В для «низкого» логического состояния и от 2, 7 до 5 вольт для «высокого» логического состояния :

Если сигнал напряжения в диапазоне от 0, 8 В до 2 вольт должен был быть отправлен на вход ТТЛ-затвора, не было бы никакого ответа от затвора. Такой сигнал будет считаться неопределенным, и ни один производитель логических ворот не будет гарантировать, что их схема затвора будет интерпретировать такой сигнал.

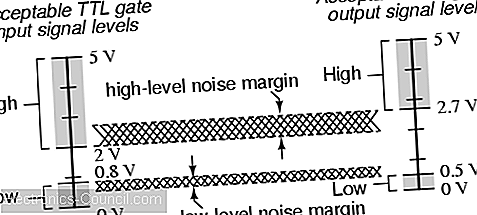

Как вы можете видеть, допустимые диапазоны для уровней выходного сигнала более узкие, чем для уровней входного сигнала, чтобы гарантировать, что любой таймер TTL, выдающий цифровой сигнал на вход другого таймера TTL, передаст напряжения, приемлемые для принимающего затвора. Разница между допустимыми диапазонами выходного и входного сигналов называется пределом шума ворот. Для TTL-ворот низкоуровневый уровень шума представляет собой разность между 0, 8 и 0, 5 вольтами (0, 3 вольта), в то время как уровень шума высокого уровня — это разность между 2, 7 вольта и 2 вольта (0, 7 вольта). Проще говоря, запас шума — это пиковое количество ложного или «шумового» напряжения, которое может быть наложено на сигнал слабого напряжения выходного напряжения до того, как принимающий вентиль может неправильно его интерпретировать:

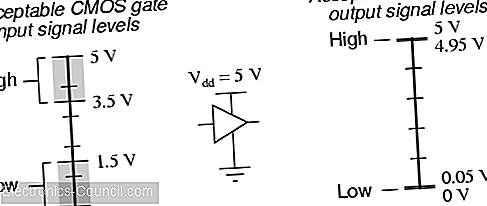

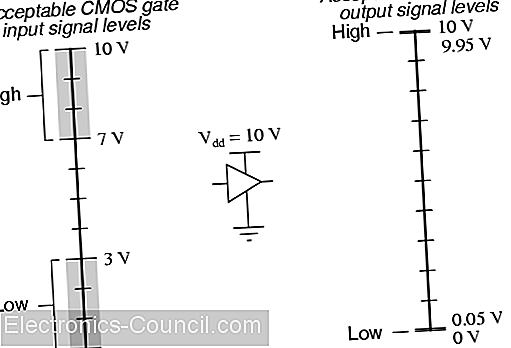

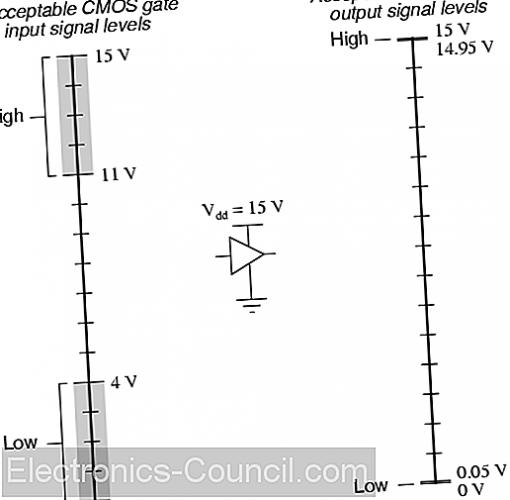

Схемы затворов CMOS имеют спецификации входных и выходных сигналов, которые сильно отличаются от TTL. Для CMOS-затвора, работающего при напряжении питания 5 вольт, допустимые значения входного сигнала варьируются от 0 вольт до 1, 5 вольт для «низкого» логического состояния и от 3, 5 до 5 вольт для «высокого» логического состояния. «Допустимые» напряжения выходного сигнала (уровни напряжения, гарантированные производителем затвора в заданном диапазоне условий нагрузки) находятся в диапазоне от 0 до 0, 05 вольт для «низкого» логического состояния и от 4, 95 до 5 вольт для «высокого» логического состояния :

Из этих цифр должно быть очевидно, что схемы затворов CMOS имеют гораздо больший предел шума, чем TTL: 1, 45 вольт для низкоуровневых и высокоуровневых полей CMOS против 0, 7 вольт для TTL. Другими словами, схемы CMOS могут переносить в два раза больше наложенного «шумового» напряжения на своих входных линиях до того, как будут получены ошибки интерпретации сигнала.

Поля шума CMOS еще больше расширяются при более высоких рабочих напряжениях. В отличие от TTL, который ограничен напряжением питания 5 В, CMOS может питаться от напряжений до 15 вольт (некоторые схемы CMOS до 18 вольт). Здесь показаны приемлемые «высокие» и «низкие» состояния для входных и выходных сигналов CMOS-интегральных схем, работающих при напряжении 10 В и 15 В соответственно:

Поля для приемлемых «высоких» и «низких» сигналов могут быть больше, чем показано на предыдущих иллюстрациях. Показанное представление представляет собой «наихудший» входной сигнал, основанный на спецификациях производителя. На практике можно обнаружить, что схема затвора будет допускать «высокие» сигналы с гораздо меньшим напряжением и «низкими» сигналами значительно большего напряжения, чем указанные здесь.

И наоборот, чрезвычайно малые значения выходного поля — гарантирующие выходные состояния для «высоких» и «низких» сигналов с точностью до 0, 05 вольт «рельсов» источника питания — оптимистичны. Такие «твердые» уровни выходного напряжения будут справедливыми только для условий минимальной нагрузки. Если затвор подает или поглощает значительный ток на нагрузку, выходное напряжение не сможет поддерживать эти оптимальные уровни из-за внутреннего сопротивления канала выходных МОП-транзисторов ворот.

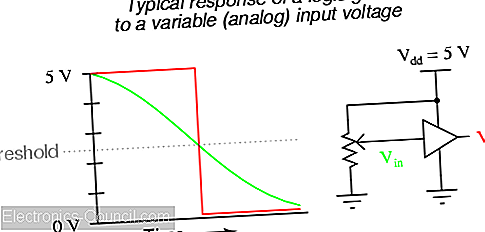

В пределах «неопределенного» диапазона для любого входа затвора будет некоторая точка демаркации, делящая фактический «низкий» диапазон входных сигналов затвора от его фактического «высокого» диапазона входных сигналов. То есть, где-то между самым низким «высоким» уровнем напряжения сигнала и наивысшим «низким» уровнем напряжения сигнала, гарантированным изготовителем затвора, существует пороговое напряжение, при котором затвор фактически переключит свою интерпретацию сигнала с «низкого» или «Высокий» или наоборот. Для большинства схем затворов это неуказанное напряжение является единственной точкой:

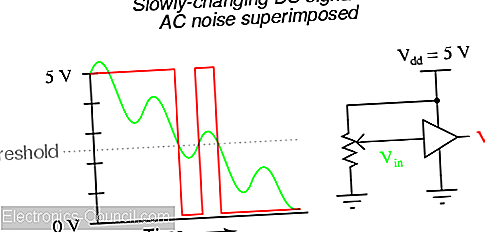

При наличии переменного напряжения «шум», наложенного на входной сигнал постоянного тока, одна пороговая точка, при которой ворота изменяет свою интерпретацию логического уровня, приведет к неустойчивому выходу:

Если этот сценарий вам знаком, это потому, что вы помните аналогичную проблему с (аналоговыми) схемами компаратора напряжения компаратора. При одной пороговой точке, при которой вход приводит к переключению между «высокими» и «низкими» состояниями, наличие значительного шума вызовет неустойчивые изменения в выходе:

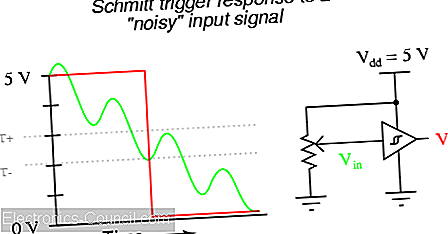

Решение этой проблемы представляет собой немного положительной обратной связи, введенной в схему усилителя. При использовании op-amp это делается путем подключения выхода обратно к неинвертирующему (+) входу через резистор. В схеме затвора это влечет за собой изменение схемы внутреннего затвора, установление обратной связи внутри пакета ворот, а не через внешние соединения. Разработанный ворот называется триггером Шмитта . Триггеры Шмитта интерпретируют изменяющиеся входные напряжения в соответствии с двумя пороговыми напряжениями: положительным порогом (V T + ) и отрицательным порогом (V T- ):

Триггерные затворы Шмитта различаются на схематичных диаграммах маленьким символом «гистерезиса», нарисованным внутри них, напоминающим кривую BH для ферромагнитного материала. Гистерезис, вызванный положительной обратной связью в схеме ворот, добавляет дополнительный уровень помехоустойчивости к характеристикам ворот. Триггерные затворы Шмитта часто используются в приложениях, где ожидается шум на входной сигнальной линии (линиях) и / или где неустойчивый выход будет очень пагубным для производительности системы.

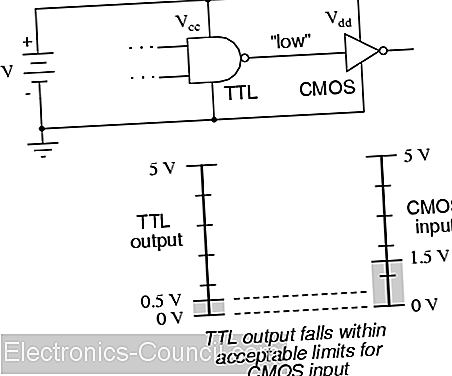

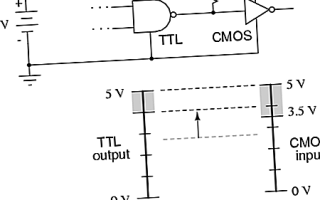

Разные требования к уровню напряжения для TTL и CMOS-технологий представляют проблемы, когда два типа ворот используются в одной и той же системе. Хотя работающие CMOS-ворота с тем же напряжением питания 5, 00 вольт, которое требуется для ворот TTL, не проблема, уровни выходного напряжения TTL не будут совместимы с требованиями к входному напряжению CMOS.

Возьмем, к примеру, затвор TTL NAND, выводящий сигнал на вход затвора инвертора CMOS. Оба вентилятора питаются от того же источника питания 5, 00 вольт (V cc ). Если затвор TTL выводит «низкий» сигнал (гарантируется, что он находится в диапазоне от 0 до 0, 5 вольта), он будет правильно интерпретирован входным сигналом CMOS в качестве «низкого» (ожидая напряжения от 0 до 1, 5 вольт):

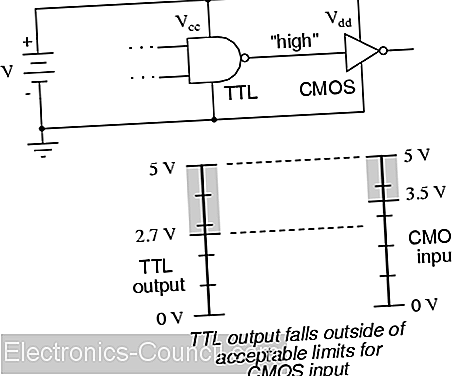

Однако, если затвор TTL выводит «высокий» сигнал (гарантируется, что он составляет от 5 вольт до 2, 7 вольта), он может быть неправильно интерпретирован входным сигналом CMOS в качестве «высокого» (ожидая напряжения от 5 до 3, 5 вольта ):

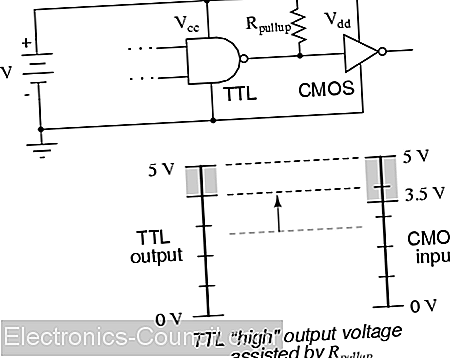

Учитывая это несоответствие, вполне возможно, что затвор TTL выдаст действительный «высокий» сигнал (действительный, то есть согласно стандартам TTL), который находится в «неопределенном» диапазоне для входа CMOS и может быть ( ложно) интерпретируется как «низкий» получающим воротом. Легким «исправлением» этой проблемы является увеличение уровня напряжения «высокого» уровня напряжения TTL с помощью подтягивающего резистора:

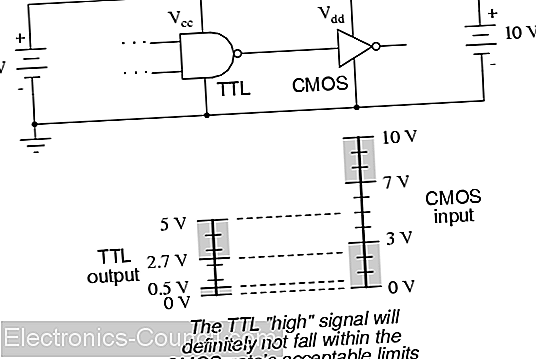

Однако необходимо что-то большее, чем это, для интерфейса TTL-выхода с входом CMOS, если принимающий затвор CMOS питается от большего напряжения питания:

Разумеется, не будет никаких проблем с затвором CMOS, который интерпретирует «низкий» выход ТТЛ-ворот, но «высокий» сигнал от затвора TTL — это совсем другое дело. Гарантированный диапазон выходного напряжения от 2, 7 вольта до 5 вольт от выхода затвора TTL нигде не приближается к допустимому диапазону затвора CMOS от 7 вольт до 10 вольт для «высокого» сигнала. Если мы используем заслонку TTL с открытым коллектором вместо выходного затвора тотемного полюса, то подтягивающий резистор к направляющей Vdd с напряжением 10 вольт повысит «высокое» выходное напряжение затвора TTL до полного напряжения питания, подающего CMOS Ворота. Поскольку затвор с открытым коллектором может поглощать ток, а не источник тока, уровень напряжения «высокого» уровня полностью определяется источником питания, к которому подключен нагрузочный резистор, тем самым аккуратно решая проблему несоответствия:

Из-за превосходных характеристик выходного напряжения для CMOS-затворов, как правило, нет проблем с подключением CMOS-выхода к входу TTL. Единственной существенной проблемой является текущая загрузка, представленная входами TTL, поскольку выход CMOS должен поглощать ток для каждого входа TTL в состоянии «низкого».

В случае, когда затвор CMOS питается от источника напряжения, превышающего 5 вольт (V cc ), проблема может возникнуть. «Высокое» состояние выхода затвора CMOS, превышающее 5 вольт, будет превышать допустимые пределы входного сигнала TTL для «высокого» сигнала. Решением этой проблемы является создание инверторной схемы с открытым коллектором с использованием дискретного транзистора NPN и использование ее для одновременного соединения двух ворот:

Резистор «R pullup » не является обязательным, так как входы TTL автоматически принимают «высокое» состояние при оставленном плавании, что и произойдет, когда выход затвора CMOS «низкий», и транзистор отключается. Конечно, одним из важных последствий реализации этого решения является логическая инверсия, создаваемая транзистором: когда затвор CMOS выводит «низкий» сигнал, TTL-вентилятор видит «высокий» вход; и когда затвор CMOS выводит «высокий» сигнал, транзистор насыщается, а TTL-вентиль видит «низкий» вход. Пока эта инверсия учитывается в логической схеме системы, все будет хорошо.

Используемые источники:

- https://mysku.ru/blog/aliexpress/72856.html

- https://ttlp.belstu.by/o-fakultete/dekanat.html

- https://ru.electronics-council.com/logic-signal-voltage-levels-67475

Автоматика для отканых ворот: дистанционное управление

Автоматика для отканых ворот: дистанционное управление

Дистанционное управление распашными воротами своими руками

Дистанционное управление распашными воротами своими руками Обзор Quadralite Reporter 200 (Godox AD200)

Обзор Quadralite Reporter 200 (Godox AD200)

Как обойти ограничение на раздачу интернета МТС

Как обойти ограничение на раздачу интернета МТС Обзор всех вспышек Yongnuo. Какую лучше выбрать в актуальном модельном ряду

Обзор всех вспышек Yongnuo. Какую лучше выбрать в актуальном модельном ряду Простой переходник USB - UART TTL

Простой переходник USB - UART TTL Как «чайник» делал UART RS232 конвертер для Orange Pi

Как «чайник» делал UART RS232 конвертер для Orange Pi